Next gEneration Architectures and TECHnologies for telecom digital processors (NEATECH)

The NEATECH project aims to develop advanced processor architectures using strategies that prioritise high integration and low power consumption. The primary goal is to significantly reduce power usage, mass, and volume while improving integration efficiency.

The project will propose processor technologies and architectures that are scalable, capable of handling high data rates, and designed for low power consumption and cost-effectiveness. Additionally, it will introduce simplified, low-complexity algorithms tailored to these architectures.

Machine learning techniques, enhanced by AI accelerators, will be integrated into the designs to deliver fast and reliable responses to the complex demands of Geostationary Orbit (GEO), Medium Earth Orbit (MEO), and Low Earth Orbit (LEO) missions.

To demonstrate the feasibility of these advancements, the project will produce a prototype showcasing the proposed architectures, processors, and algorithms for the most critical technologies and functions.

The project at a glance

About

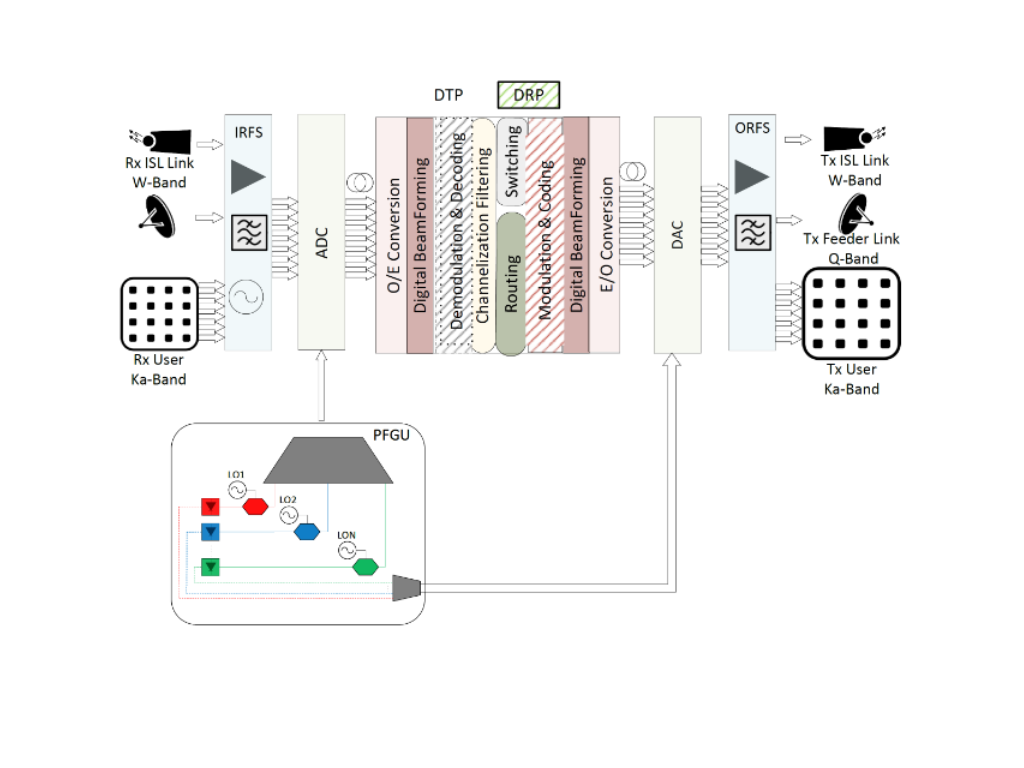

The NEATECH project focuses on advancing digital processor technologies for satellite payloads to address the increasing complexity of modern satellite missions. Digital processors are vital for managing various communication functions, such as channelisation, regenerative processing, routing, switching, and beamforming, as shown in the accompanying figure. However, integrating these capabilities into a single, power-efficient framework presents significant technical challenges.

To tackle these challenges, NEATECH aims to develop innovative digital processor architectures that prioritise high integration and low power consumption. The project seeks to reduce power usage, mass, and volume while improving scalability and data rate performance, redefining the standard for digital processors in satellite missions. A key aspect of this effort is the integration of machine learning techniques and AI accelerators, enabling reliable and fast responses to the demands of Geostationary Orbit (GEO), Medium Earth Orbit (MEO), and Low Earth Orbit (LEO) missions.

The project begins by consolidating requirements for digital telecom processors and defining mission scenarios to guide development. It will evaluate state-of-the-art integration techniques, such as photonics processing, to identify the most promising architectures for improving efficiency. A thorough assessment of existing and emerging processor technologies will establish baseline architectures, which will be tested against performance criteria for scalability, power consumption, and readiness for mission deployment.

A key milestone for NEATECH is the creation of a prototype that demonstrates the proposed processor architecture and algorithms. This prototype will undergo rigorous testing to validate its performance under real-world mission conditions. Additionally, the project will deliver a Technology Roadmap, outlining future directions for satellite communication applications.

By driving innovation in digital processor design, NEATECH aims to enable smarter, more efficient satellite systems capable of meeting the growing demands for higher data rates, intelligent resource allocation, and sustainable operation in space-constrained environments. The project’s outcomes will lay the foundation for next-generation satellite communication technologies, delivering enhanced performance and cost-effectiveness for future missions.

Organisation and Partners

European Space Agency

Interdisciplinary Centre for Security, Reliability and Trust (SnT)

Fonds National Recherche (FNR)

Project team

Keywords

Beamforming

Satellite Communications

Onboard Processors

Antenna Design